对于初画PCB的人来说,当把原理图中封装信息导入到PCB,看到密密麻麻那么多线,纵横交错,感觉就无从下手;所以为了帮助初学者快速入门,现在我就从布局和布线两个方面做一个简单说明!

一 、布局

1、 一般布局PCB,我们会遵循“先大后小,先难后易”的布置原则,也就是说我们一般先去布局重要单元电路,以及核心器件,比如MCU最小系统、高频高速模块电路,这些都可以理解为重要单元电路;

2 、布局中需要参考原理图框图,可以先把原理图中各个单元电路先布局好,到时候整体在进行拼凑,当然拼抽的时候,要考虑电路信号的主提走向;

3 、布局应尽量满足以下要求:总的连线尽可能短,关键信号线最短;高电压、大电流信号与小电流,低电压的弱信号完全分开;模拟信号与数字信号分开;高频信号与低频信号分开;高频元器件的间隔要充分。

4 、去耦电容的布局要尽可能靠近IC的电源管脚,并且保证电源与地之间形成的回路最短,当然为了达到去耦最佳效果,电源与地需经过去耦电容两端,然后再连接到IC电源和地两端;

5 、对于一些需要过静电测试的产品,其器件放置尽量离板边缘距离大于3.5mm;如果板子空间有限,可以在离板边缘大于0.45mm出打过孔到地;

6 、在完成板子性能的基础下,布局中就需要考虑美观,对于相同结构的电路部分,尽可能采用"对称式“布局,总体布局可以按照”均匀分布,重心平衡,版面美观“的标准;

7 、 对于发热器件,比如MOS管,可以采取加散热片的形式,给予散热;

二 、 布线

1 、地走线线径>电源走线线径>信号走线线径,对于1盎司铜厚的板子,我们会预计1mm走线宽度能走1A电流

2、 对于信号线走线,我们一般会优先走模拟小信号、高速信号、高频信号、时钟信号;其次再走数字信号;

3 、晶振周围尽量禁空,尤其其底部禁止走线;且应远离板上的电源部分,以防止电源和时钟相互干扰;

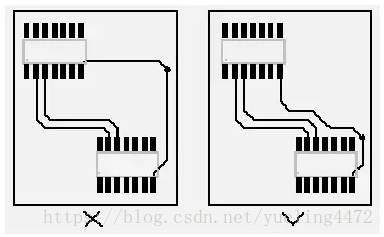

4 、 避免直角走线 、锐角走线,因为直角、锐角走线会使得传输线的线宽产生变化,造成其阻抗的不连续。如果进行直角走线其拐角可以等效为传输线上的容性负载,减缓上升时间,在高速、高频中就变得尤为明显,而且其造成的阻抗不连续,还会增加信号的反射;其直角尖端还为产生EMI;

5 、对于模拟信号和数字信号应尽量分块布线,不宜交叉或混在一起,对于其模拟地和数字地也应用磁珠或者0R电阻进行隔离;

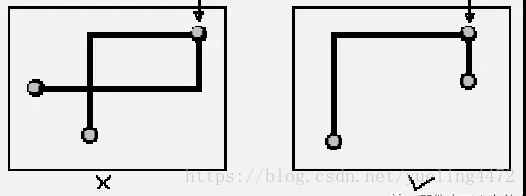

6 、地线回路环路保持最小,即信号线与其回路构成的环面积要尽可能小,环面积越小,对外的辐射越少,接收外界的干扰也越小。 对于top层和bottom层敷地的时候,需要仔细查看,有些信号地是否被信号线分割,造成地回路过远,此时应该在分割处打过孔,保证其地回路尽可能小;

7 、 为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持70%的电场不互相干扰,称为3W规则。如要达到98%的电场不互相干扰,可使用10W的间距 ;

8 、 信号线的长度避免为所关心频率的四分之一波长的整数倍,否则此信号线会产生谐振,谐振时信号线会产生较强的辐射干扰;

9 、信号走线禁止走成环形,其环形容易形成环形天线,产生较强的辐射干扰;

10 、 对于天线ANT端走线应尽量短而直,其阻抗也应通过 SI9000 去计算,保证其线阻为50欧姆(一般天线端口走线为50欧姆);

11 、敷铜时,对其焊盘引脚应采用十字焊盘,不宜采用实心焊盘敷铜,这样在生产时候,器件容易立碑;

13642342920